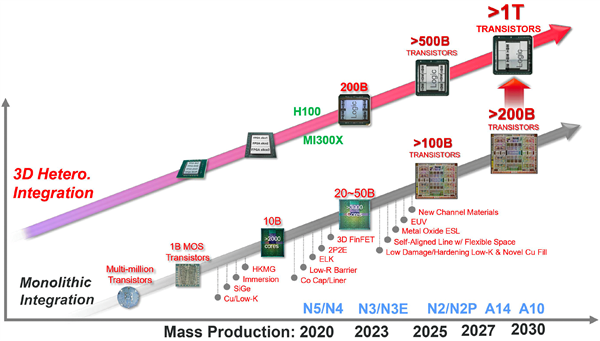

����IEDM 2023���ʵ���Ԫ�������ϣ�̨���繫����һ��Ұ�IJ����İ뵼�����칤�ա���װ����·��ͼ���Ѿ��滮����2030�ꡣ

�������£�̨���������ƽ�3nm�����N3ϵ�й��գ���һ��������2025-2027����̿�2nm�����N2ϵ�У�����N2��N2P�ȣ����ڵ���оƬ�ڼ��ɳ���1000�ڸ�����ܣ�������װ��������������5000�ڸ���

����Ϊ�ˣ�̨���罫ʹ��EUV�������̡���ͨ�����ϡ�����������ESL���Զ����ߵ��Կռ䡢�����˵�Ӳ����Kͭ�������ȵ�һϵ���²��ϡ��¼����������CoWoS��InFO��SoIC��һϵ�з�װ������

�������������1.4nm�����A14��1nm�����A10——������Intel A20��A18���һ�ޣ�����������“�Ƚ�”��

����1nm A10���սڵ�ƻ�2030���������������ڵ���оƬ�ڼ��ɳ���2000�ڸ�����ܣ�������װ����1���ڸ������N2���շ�һ����

������Ȥ���ǣ�IntelҲ�ƻ���2030������������װ1���ڸ����������ν�����ԡ�

����Ŀǰ��ӵĵ�оƬ��NVIDIA GH100������ܴ�800�ڸ���

������оƬ��װ���洦�����ȵ�λ���Ǹ���GPU����оƬ��Intel Ponte Vecchio GPU Max����1000�ڸ�����ܣ�AMD Instinct MI300A��MI300X�ֱ���1460�ڸ���1530�ڸ�����ܡ�